HDL语言仿真软件Mentor Graphics ModelSim SE 2021.1 x64 许可授权激活版

- 大小:778MB

- 分类:编程工具

- 环境:Windows

- 更新:2021-12-27

热门排行

简介

ModelSim SE免费许可版是业界最优秀的HDL语言仿真器,它是统一的调试和仿真环境,可在生产性工作环境中为当今的FPGA设计人员提供先进的功能,除了支持标准HDL,ModelSim还提高了设计质量和调试效率。ModelSim屡获殊荣的Single Kernel Simulator(SKS)技术可在一个设计中透明混合VHDL和Verilog。它的体系结构允许独立于平台的编译以及本机编译代码的出色性能。图形用户界面功能强大,一致且直观。在其他任何窗口中的活动之后,所有窗口都会自动更新。例如,在结构窗口中选择一个设计区域会自动更新源,信号,过程和变量窗口。您可以在不离开ModelSim环境的情况下进行编辑,重新编译和重新仿真。所有用户界面操作都可以编写脚本,并且仿真可以批处理或交互模式运行。ModelSim以标准延迟格式(SDF)提供的时序模拟行为,RTL和门级代码,包括VHDL VITAL和Verilog门库。ModelSim易于使用,统一的调试和仿真环境为当今的FPGA设计人员提供了在生产性工作环境中的高级功能。

PS:本次为大家提供的是最新ModelSim SE最新激活版下载地址,包含有效破解补丁,欢迎需要此款工具的朋友前来下载使用。

基本介绍

Mentor Graphics 是第一个将单内核模拟器(SKS)技术与用于Verilog,VHDL和SystemC的统一调试环境结合在一起的公司。业界领先的本地SKS性能与最佳的集成调试和分析环境相结合,使ModelSim成为ASIC和FPGA设计的首选模拟器。业界最佳的标准和平台支持使其易于在大多数流程和工具流程中采用。

通过智能设计的调试环境,ModelSim简化了查找设计缺陷的过程。

ModelSim HDL仿真器为FPGA客户提供了一种简便且经济高效的方式来加速FPGA开发和测试。许多FPGA设计人员在对设计进行充分审查之前先去实验室。这意味着实验室中的调试时间可能浪费数周甚至数月。通过仿真,调试循环要快得多,并且可以完全了解设计中的信号。通过仿真,可以在进入实验室之前进行更高质量的FPGA设计,从而使在实验室上花费的时间更加高效和专注。

除了支持标准HDL,ModelSim还提高了设计质量和调试效率。ModelSim屡获殊荣的Single Kernel Simulator(SKS)技术可在一个设计中实现VHDL和Verilog的透明混合。它的体系结构允许独立于平台的编译以及本机编译代码的出色性能。

ModelSim调试环境可有效显示设计数据,以分析和调试所有语言。ModelSim允许在保存后的结果以及实时仿真运行过程中使用许多调试和分析功能。

ModelSim与Mentor的旗舰模拟器Questa共享一个公共前端和用户界面。如果需要更高的性能和对高级验证功能的支持,这可使客户轻松升级到Questa。

ModelSim SE-64安装授权教程

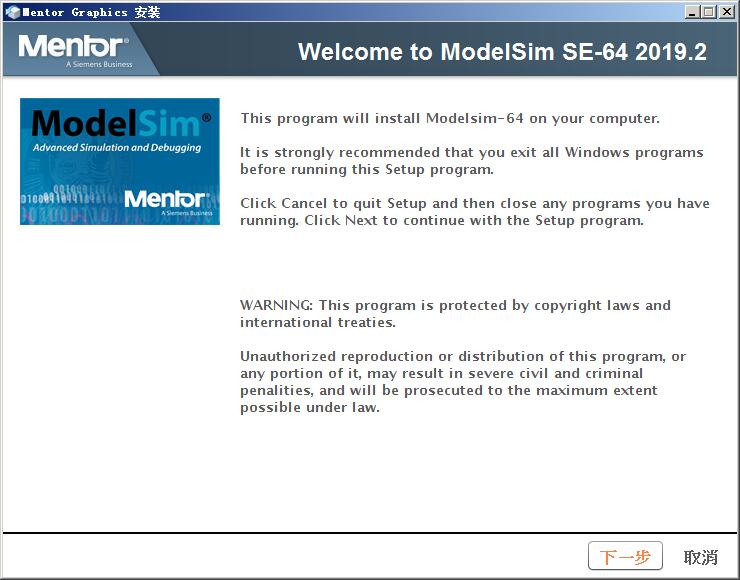

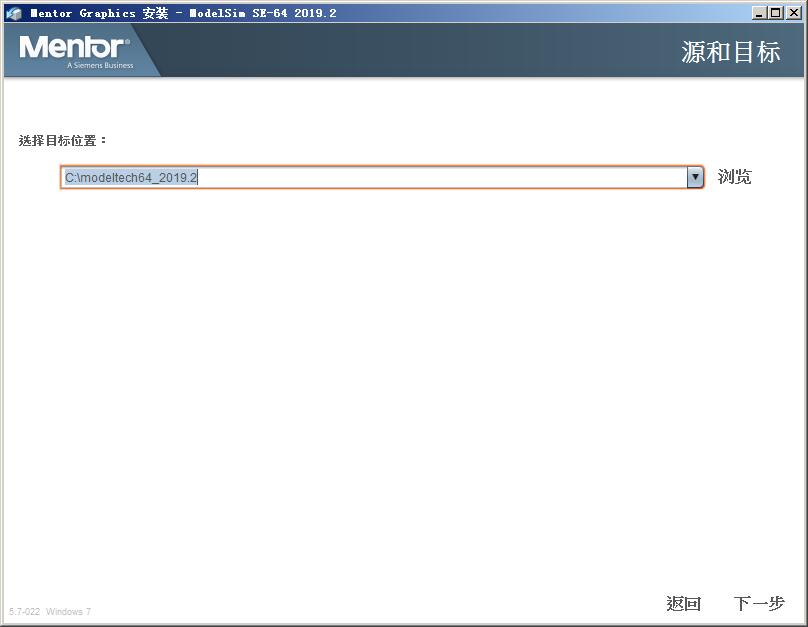

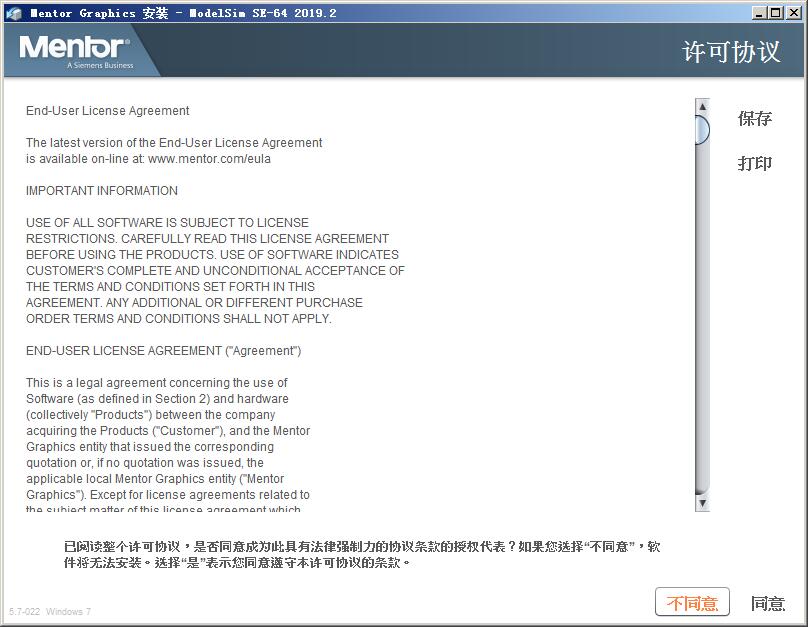

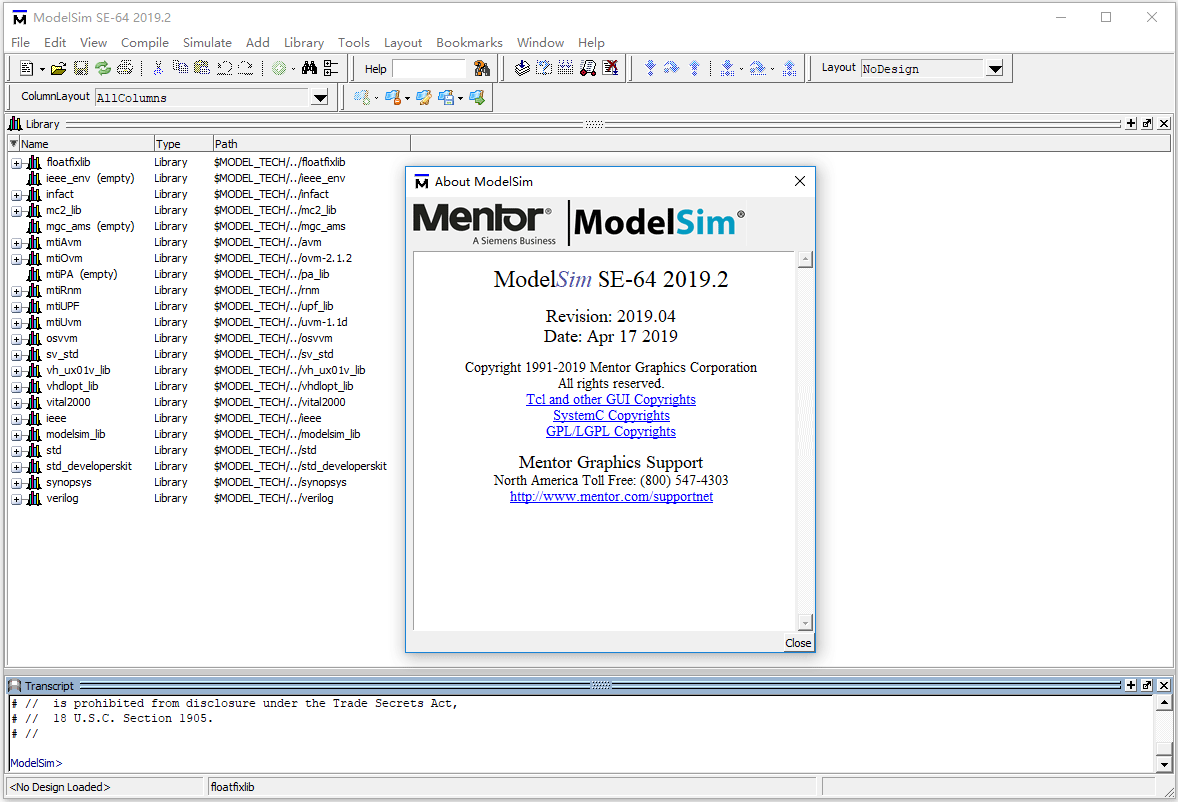

参考2019版本图,步骤是一样的

1、双击“modelsim-win64-2020.4-se.exe”开始解压安装包

2、加载完成后进入到ModelSim SE-64 2020的安装向导界面

3、继续下一步选择软件安装目录,默认为“C:\modeltech64_2020.4”

4、提示目录不存在是否创建,点击是

5、出现软件的许可协议,点击同意继续

6、然后就会开始ModelSim SE-64 2020的安装了

7、稍等一会儿就会完成软件的安装了

8、复制Crack所有文件到C:\modeltech64_2020.4\win64【默认路径】

运行patch64_dll.bat,将生成的许可证另存为LICENSE.TXT,保存一个指定位置

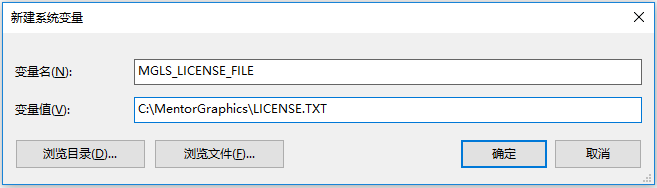

9、建系统环境变量:

变量名:LM_LICENSE_FILE

变量值:LICENSE.TXT的路径。

10、授权完成,Enjoy

更新日志

ModelSim 2020.4的发行说明-日期:2020年10月13日

在2020.4中修复了SystemVerilog缺陷-QSIM

-64132-Vlog有时会给出错误的错误,例如:

-**错误:解析文件test.sv(50)时:找不到名称'get_type '在范围'tpkg'中

-对于类似'pkg :: typename :: get_type()的名称,其中“ typename”是解析为类的typedef名称。

-QSIM-64922-Vlog报告了错误:

-**错误:test.sv(7)在Implements子句中非法引用了接口类型C :: Intf。

-如果“ C”是参数化的类类型,而“ Intf”是引用接口类的typedef名称,则

在2020.4中修复了VHDL缺陷-QSIM

-65962-如果在编译时使用-autoorder和-quiet开关,如果语义错误在刷新阶段遇到错误,将不会打印错误。此行为是不正确的,并且现在打印了所有错误,尽管其他编译日志消息也被禁止

-QSIM-66278-如果占用超过2G的空间的大型数据结构将崩溃使用默认初始化。为此,数据结构中所有字段的默认值必须为0或NULL。显式初始化对象将解决此问题。

-QSIM-65639-design.bin的信号范围可能不正确。如果信号范围取决于函数调用,则会发生这种情况。这些函数使用std.textio。

chrome下载

chrome下载 知乎下载

知乎下载 Kimi下载

Kimi下载 微信下载

微信下载 天猫下载

天猫下载 百度地图下载

百度地图下载 携程下载

携程下载 QQ音乐下载

QQ音乐下载